## Lecture Notes in Computer Science

4782

Commenced Publication in 1973

Founding and Former Series Editors:

Gerhard Goos, Juris Hartmanis, and Jan van Leeuwen

#### **Editorial Board**

David Hutchison

Lancaster University, UK

Takeo Kanade

Carnegie Mellon University, Pittsburgh, PA, USA

Josef Kittler

University of Surrey, Guildford, UK

Jon M. Kleinberg

Cornell University, Ithaca, NY, USA

Friedemann Mattern

ETH Zurich, Switzerland

John C. Mitchell

Stanford University, CA, USA

Moni Naor

Weizmann Institute of Science, Rehovot, Israel

Oscar Nierstrasz

University of Bern, Switzerland

C. Pandu Rangan

Indian Institute of Technology, Madras, India

Bernhard Steffen

University of Dortmund, Germany

Madhu Sudan

Massachusetts Institute of Technology, MA, USA

Demetri Terzopoulos

University of California, Los Angeles, CA, USA

Doug Tygar

University of California, Berkeley, CA, USA

Moshe Y. Vardi

Rice University, Houston, TX, USA

Gerhard Weikum

Max-Planck Institute of Computer Science, Saarbruecken, Germany

Ronald Perrott Barbara M. Chapman Jaspal Subhlok Rodrigo Fernandes de Mello Laurence T. Yang (Eds.)

# High Performance Computing and Communications

Third International Conference, HPCC 2007 Houston, USA, September 26-28, 2007 Proceedings

#### Volume Editors

Ronald Perrott Queen's University Belfast Belfast, UK

E-mail: r.perrott@qub.ac.uk

Barbara M. Chapman University of Houston Houston TX 77004, USA E-mail: chapman@cs.uh.edu

Jaspal Subhlok University of Houston, Houston TX 77204, USA E-mail: jaspal@cs.uh.edu

Rodrigo Fernandes de Mello University of São Paulo CEP 13560-970 São Carlos, SP, Brazil

E-mail: mello@icmc.usp.br

Laurence T. Yang St. Francis Xavier University Antigonish, NS, Canada E-mail: lyang@stfx.ca

Library of Congress Control Number: 2007936289

CR Subject Classification (1998): D.2, F.1-2, C.2, G.1-2, H.4-5

LNCS Sublibrary: SL 1 – Theoretical Computer Science and General Issues

ISSN 0302-9743

ISBN-10 3-540-75443-1 Springer Berlin Heidelberg New York ISBN-13 978-3-540-75443-5 Springer Berlin Heidelberg New York

This work is subject to copyright. All rights are reserved, whether the whole or part of the material is concerned, specifically the rights of translation, reprinting, re-use of illustrations, recitation, broadcasting, reproduction on microfilms or in any other way, and storage in data banks. Duplication of this publication or parts thereof is permitted only under the provisions of the German Copyright Law of September 9, 1965, in its current version, and permission for use must always be obtained from Springer. Violations are liable to prosecution under the German Copyright Law.

Springer is a part of Springer Science+Business Media

springer.com

© Springer-Verlag Berlin Heidelberg 2007 Printed in Germany

Typesetting: Camera-ready by author, data conversion by Scientific Publishing Services, Chennai, India Printed on acid-free paper SPIN: 12169436 06/3180 5 4 3 2 1 0

## **Preface**

Welcome to the proceedings of the 2007 International Conference on High Performance Computing and Communications (HPCC 2007), which was held in Houston, Texas, USA, September 26–28, 2007.

There have been many exciting developments in all aspects of HPC over the last decade and more exciting developments are on the horizon with, for example, the petaflops performance barrier being targeted in the near future. The rapid expansion in computing and communications technology has stimulated the growth of powerful parallel and distributed systems with an ever increasing demand for HPC in many disciplines. This, in turn, has increased the requirements for more reliable software, better algorithms, more comprehensive models and simulations and represents a challenge to the HPC community to produce better tools, research new areas, etc. Hence conferences, like HPCC 2007, play an important role in enabling engineers and scientists to come together in order to address all HPC-related challenges and to present and discuss their ideas, research results and applications experience.

This year there were 272 paper submissions from all across the world, not only from Europe, North America and South America but also from Asia and the Pacific. All the papers were reviewed by at least three referees from the conference's technical program committee or their colleagues. In order to allocate as many papers as possible and keep the high quality of the conference, we finally decided to accept 69 papers for the conference, which represented the acceptance rate of 25%. We believe that all of these papers and topics not only provide novel ideas, new results, work in progress and state-of-the-art techniques in this field, but will also stimulate future research activities in the area of high performance computing and communications.

This conference is a result of the hard work of very many people such as the program vice chairs, the external reviewers and the program and technical committee members. We would like to express our sincere thanks to everyone involved. Ultimately, however, the success of the conference will be judged by how well the delegates have participated, learnt, interacted and established contacts with other researchers. The committees have provided the venue and created the environment to allow these objectives to be achieved. It is now up to all of us to ensure that the conference is an outstanding success.

We wish you a successful, stimulating and rewarding conference and look forward to seeing you again at future HPCC conferences.

August 2007

Ronald Perrott Barbara Chapman Jaspal Subhlok Rodrigo Fernandes de Mello Laurence Tianruo Yang

## Organization

## **Executive Committee**

General Chairs Barbara Chapman, University of Houston, USA

Jaspal Subhlok, University of Houston, USA

Program Chair Ronald Perrott, Queens University of Belfast, UK

Program Vice Chairs Vassil Alexandrov, University of Reading, UK

Francois Bodin, University Rennes 1, France Peter Brezany, University of Vienna, Austria Marian Bubak, CYFRONET AGH, Poland

Michel Diaz, LAAS, France

Edgar Gabriel, University of Houston, USA

Laurent Lefevre, École Normale Supérieure de Lyon,

France

Yunhao Liu, Hong Kong University of Science

Technology, China

Erik Maehle, University of Luebeck, Germany Allen Malony, University of Oregon, USA

Thomas Rauber, University of Bayreuth, Germany

Martin Schulz, Lawrence Livermore National

Laboratory, USA

Alan Sussman, University of Maryland, USA Roland Wismüller, University of Siegen, Germany Hans Zima, California Institute of Technology, USA

Steering Chairs Beniamino Di Martino, Seconda Università di

Napoli, Italy

Laurence T. Yang, St. Francis Xavier University,

Canada

Publication Chair Rodrigo Fernandes de Mello, University of São Paulo,

Brazil

Web Chairs Rodrigo Fernandes de Mello, University of São Paulo,

Brazil

Tony Li Xu, St. Francis Xavier University, Canada Liu Yang, St. Francis Xavier University, Canada

Local Organizing Chair Rosalinda Mendez, University of Houston, USA

## **Sponsoring Institutions**

Sun Microsystems

## Program Committee

David Abramson Monash University, Australia Raad S. Al-Qassas University of Glasgow, UK Vassil Alexandrov University of Reading, UK

Henrique Andrade IBM Thomas J. Watson Research Laboratory, USA

Cosimo Anglano University of Alessandria, Italy

Irfan Awan University of Bradford, UK

Frank Ball Bournemouth University, UK

Purushotham Bangalore University of Alabama, USA

Ioana Banicescu Mississippi State University, USA

Alessandro Bassi Hitachi Europe, France

Alessio Bechini University of Pisa, Italy

Micah Beck University of Tennessee, USA

Siegfried Benkner University of Vienna, Austria

Arndt Bode Technische Universität München, Germany

Francois Bodin University of Rennes 1, France Luciano Bononi University of Bologna, Italy George Bosilca University of Tennessee, USA University of Vienna, Austria Peter Brezany CYFRONET AGH, Poland Marian Bubak Wojciech Burakowski Warsaw University, Poland Fabian Bustamante Northwestern University, USA Armando Caro BBN Technologies, USA

Calin Cascaval IBM Thomas J. Watson Research Center, USA

Umit Catalyurek Ohio State University, USA

Bradford Chamberlain Cray Inc., USA

Guihai Chen Nanjing University, China

Lei Chen Hong Kong University of Science and Technology,

China

I-hsin Chung IBM Research, USA

Toni Cortes Universitat Politècnica de Catalunya, Spain

Marilia Curado University of Coimbra, Portugal Khuzaima Daudjee University of Waterloo, Canada Geert Deconinck University of Leuven, Belgium

Frederic Desprez INRIA, France Michel Diaz LAAS, France

Ivan Dimov University of Reading, UK Karim Djemame University of Leeds, UK

Andreas Doering IBM Research at Zurich, Switzerland

Werner Dubitzky University of Ulster, UK

Olivier Dugeon France Telecom, France

Marc Duranton NXP Semiconductors, The Netherlands

Ernesto Exposito University of Toulouse, France

Wu Feng Virginia Polytechnic Institute and State University,

USA

Robert J. Fowler University of North Carolina at Chapel Hill, USA

Karl Fuerlinger University of Tennessee, USA

Edgar Gabriel University of Houston, USA

Alex Galis University College London, UK

Daniel Rodriguez Garcia

Jean-Patrick Gelas University Lyon 1, France

Michael Gerndt Technical University of Munich, Germany

Luc Giraud ENSEEIHT, France

Olivier Gluck École Normale Supérieure de Lyon, France

Andrzej M. Goscinski Deakin University, Australia

Georgios Goumas National Technical University of Athens, Greece

Anastasios Gounaris University of Manchester, UK William Gropp Argonne National Laboratory, USA

Karl-Erwin Grosspietsch Fraunhofer Institute for Autonomous Intelligent

Systems, Germany

Tao Gu Institute for Infocomm Research, Singapore

Abdelkader Hameurlain University of Paul Sabatier, France

Jinsong Han Hong Kong University of Science and Technology,

China

Hermann Hellwagner University Klagenfurt, Austria Jano van Hemert National e-Science Centre, UK Jeff Hollingsworth University of Maryland, USA Chunming Hu Beihang University, China

Tai-Yi Huang National Tsing Hua University, Taiwan Zhiyi Huang University of Otago, New Zealand

Marty Humphrey University of Virginia, USA

Toshiyuki Imamura The University of Electro Communications, Japan Zhen Jiang West Chester University of Pennsylvania, USA Hai Jin Huazhong University of Science and Technology,

China

Helen Karatza Aristotle University of Thessaloniki, Greece

Karen Karavanic Portland State University, USA

Constantine Katsinis Drexel University, USA

Joerg Keller University of Hagen, Ge-

Joerg Keller University of Hagen, Germany Rainer Keller University of Stuttgart, Germany Christoph Kessler Linköping University, Sweden

Nectarios Koziris National Technical University of Athens, Greece

Jean-Christophe Lapayre University of Franche-Comté, France Jenq-Kuen Lee National Tsing-Hua University, Taiwan Wang-Chien Lee The Pennsylvania State University, USA Laurent Lefevre École Normale Supérieure de Lyon, France Rainer Leupers Aachen University of Technology, Germany

Xiuqi Li Florida Atlantic University, USA Yiming Li National Chiao Tung University, Taiwan

Jie Lian University of Waterloo, Canada

Xiaofei Liao Huazhong University of Science and Technology,

China

Wei Lin Australian Taxation Office, Australia

Yunhao Liu Hong Kong University of Science and Technology,

China

David Lowenthal University of Georgia, USA

Janardhan Lyengar Connecticut College, USA

Erik Maehle University of Luebeck, Germany

Allen Malony University of Oregon, USA

Muneer Masadah University of Glasgow, UK

John May Lawrence Livermore National Laboratory, USA

Eduard Mehofer University of Vienna, Austria

Piyush Mehrotra NASA AMES Research Center, USA

Alba C. M. A. de Melo University of Brasilia, Brazil

Xiaoqiao Meng University of California at Los Angeles, USA

Edmundo Monteiro University of Coimbra, Portugal Shirley Moore University of Tennessee, USA

Matthias Mueller Technical University of Dresden, Germany

Henk Muller University of Bristol, UK

Lenka Novakova Czech Technical University, Czech Republic

John O'Donnell University of Glasgow, UK

Gabriel Oksa Slovak Academy of Sciences, Slovak Republic Vincent Oria New Jersey Institute of Technology, USA

Mohamed Ould-Khaoua University of Glasgow, UK

Béatrice Paillassa Centre National de la Recherche Scientifique, France

Lei Pan California Institute of Technology, USA

Stylianos Papanastasiou University of Glasgow, UK Steve Parker University of Utah, USA

Rubem Pereira Liverpool John Moores University, UK

Cong-Duc Pham University of Pau, France

Jean-Marc Pierson University Paul Sabatier, France

Gilles Pokam University of California at San Diego, USA

Balakrishna Prabhu VTT Technical Research Centre of Finland, Finland

Isabelle Puaut University of Rennes, France

Khaled Ragab Ain Shams University, Egypt

Massimiliano Rak Seconda Università di Napoli, Italy

Raul Ramirez-Velarde

Andrew Rau-Chaplin

Thomas Rauber

Monterrey Tech, Mexico

Dalhousie University, Canada

University of Bayreuth, Germany

Paul Roe Queensland University of Technology, Australia

Philip C. Roth Oak Ridge National Laboratory, USA

Gudula Ruenger Technische Universität Chemnitz, Germany

Silvius Rus Google, USA

Miguel Santana STMicroelectronics, France Erich Schikuta University of Vienna, Austria

Martin Schulz Lawrence Livermore National Laboratory, USA

Assaf Schuster Israel Institute of Technology, Israel

Stephen L. Scott Oak Ridge National Laboratory, USA

Hadi S. Shahhoseini Iran University of Science Technology, Iran

Jackie Silcock Deakin University, Australia

Peter Sobe University of Luebeck, Germany

Matt Sottile Los Alamos National Laboratory, USA

Jeff Squyres Cisco Systems, USA

Thomas Sterling California Institute of Technology, USA

Vaidy Sunderam Emory University, USA

Bronis R. de Supinski Lawrence Livermore National Laboratory, USA

Alan Sussman

Martin Swany

Domenico Talia

Kun Tan

David Taniar

Jie Tao

University of Maryland, USA

University of Delaware, USA

Università della Calabria, Italy

Microsoft Research, China

Monash University, Australia

Universität Karlsruhe, Germany

Patricia J. Teller The University of Texas at El Paso, USA

Nigel A. Thomas University of Newcastle, UK

Bernard Tourancheau University of Lyon 1, France

Shmuel Ur IBM Haifa Labs, Israel

Sudharshan Vazhkudai Oak Ridge National Laboratory, USA

Pascale Vicat-Blanc École Normale Supérieure de Lyon, France

Luis J. G. Villalba Complutense University of Madrid, Spain

Xiaofang Wang Villanova University, USA

Greg Watson Los Alamos National Laboratory, USA Josef Weidendorfer Technische Universität München, Germany

Andrew L. Wendelborn University of Adelaide, Australia Roland Wismüller University of Siegen, Germany Alexander Woehrer University of Vienna, Austria

Wolfram Woess Johannes Kepler University of Linz, Austria

Felix Wolf RWTH Aachen University, Germany Joachim Worringen Dolphin Interconnect Solutions, Germany

Dan Wu University of Windsor, Canada Tao Xie San Diego State University, USA Baijian Yang Ball State University, USA Kun Yang University of Essex, UK

Wai Gen Yee Illinois Institute of Technology, USA

Hao Yin Tsinghua University, China

Hao Yu IBM Thomas J. Watson Research Center, USA

#### XII Organization

Hongbo Zhou Slippery Rock University, USA

Hans Zima California Institute of Technology, USA

Anna Zygmunt University of Science and Technology in Krakow,

Poland

#### Additional Reviewers

Sarala Arunagiri Urtzi Ayesta Amitabha Banerjee Puri Bangalore Alessandro Bardine Véronique Baudin Andrzej Beben Daniel Becker

Ehtesham-ul-haq Dar Ibrahim Elsaved

Colin Enticott Nick Falkner Mauro Gaio Antoine Gallais

Lei Gao

Karl-Erwin Grosspietsch

Karim Guennoun Yuzhang Han Ivan Janciak Fakhri Alam Khan

Yann Labit Rui Li

Rodrigo Fernandes de Mello

Olivier Mornard Philippe Owezarski Wei Peng Kathrin Peter Vincent Roca Charles Ross Barry Rountree A.B.M. Russel Jean-Luc Scharbarg Hanno Scharwächter

Weihua Sheng

Ke Shi Abdellatif Slim Shaoxu Song Matthew Sottile Jefferson Tan Cédric Tedeschi Carsten Trinitis

Nicolas Van Wambeke

Richard Vuduc Qiang Wang Song Wu Pingpeng Yuan Jinglan Zhang

Cammy Yongzhen Zhuang

Deging Zou

## Table of Contents

# Keynote Speech

| Programming Challenges for Petascale and Multicore Parallel Systems                                  | 1  |

|------------------------------------------------------------------------------------------------------|----|

| Towards Enhancing OpenMP Expressiveness and Performance                                              | 2  |

| Bandwidth-Aware Design of Large-Scale Clusters for Scientific Computations                           | 3  |

| OpenMP 3.0 – A Preview of the Upcoming Standard                                                      | 4  |

| Manycores in the Future                                                                              | 5  |

| The Changing Impact of Semiconductor Technology on Processor Architecture                            | 6  |

| Cluster Computing                                                                                    |    |

| A Windows-Based Parallel File System                                                                 | 7  |

| PARMI: A Publish/Subscribe Based Asynchronous RMI Framework for Cluster Computing                    | 19 |

| Coarse-Grain Time Slicing with Resource-Share Control in Parallel-Job Scheduling                     | 30 |

| Quality Assurance for Clusters: Acceptance-, Stress-, and Burn-In Tests for General Purpose Clusters | 44 |

| Performance Evaluation of Distributed Computing over Heterogeneous  Networks                         | 53 |

| Data Mining, Management and Optimization                                                                                              |     |

|---------------------------------------------------------------------------------------------------------------------------------------|-----|

| Hybrid Line Search for Multiobjective Optimization                                                                                    | 62  |

| Continuous Adaptive Outlier Detection on Distributed Data Streams Liang Su, Weihong Han, Shuqiang Yang, Peng Zou, and Yan Jia         | 74  |

| A Data Imputation Model in Sensor Databases                                                                                           | 86  |

| An Adaptive Parallel Hierarchical Clustering Algorithm                                                                                | 97  |

| Distributed, Mobile and Pervasive Systems                                                                                             |     |

| Resource Aggregation and Workflow with Webcom                                                                                         | 108 |

| Performance Evaluation of View-Oriented Parallel Programming on<br>Cluster of Computers                                               | 120 |

| Maximum-Objective-Trust Clustering Solution and Analysis in Mobile Ad Hoc Networks                                                    | 132 |

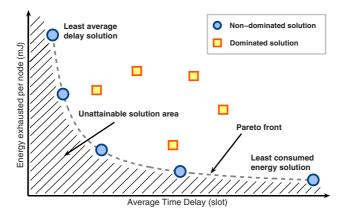

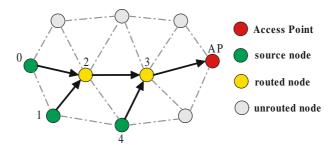

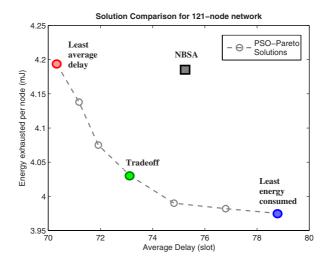

| A New Method for Multi-objective TDMA Scheduling in Wireless Sensor Networks Using Pareto-Based PSO and Fuzzy Comprehensive Judgement | 144 |

| Embedded Systems                                                                                                                      |     |

| Energy-Aware Online Algorithm to Satisfy Sampling Rates with Guaranteed Probability for Sensor Applications                           | 156 |

| A Low-Power Globally Synchronous Locally Asynchronous FFT Processor                                                                   | 168 |

| Parallel Genetic Algorithms for DVS Scheduling of Distributed Embedded Systems                                                        | 180 |

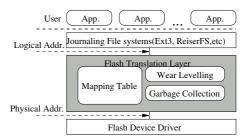

| Journal Remap-Based FTL for Journaling File System with Flash Memory                                                                  | 192 |

## **Grid Computing**

| A Complex Network-Based Approach for Job Scheduling in Grid Environments                                    | Դ4 |

|-------------------------------------------------------------------------------------------------------------|----|

| Renato P. Ishii, Rodrigo F. de Mello, and Laurence T. Yang                                                  | ,, |

| Parallel Database Sort and Join Operations Revisited on Grids 21  Werner Mach and Erich Schikuta            | 16 |

| Performance Prediction Based Resource Selection in Grid Environments                                        | 28 |

| Online Algorithms for Single Machine Schedulers to Support Advance Reservations from Grid Jobs              | 39 |

| CROWN FlowEngine: A GPEL-Based Grid Workflow Engine 24  Jin Zeng, Zongxia Du, Chunming Hu, and Jinpeng Huai | 49 |

| Dynamic System-Wide Reconfiguration of Grid Deployments in Response to Intrusion Detections                 | 30 |

| File and Memory Security Analysis for Grid Systems                                                          | 73 |

| Business Model and the Policy of Mapping Light Communication Grid-Based Workflow Within the SLA Context     | 35 |

| The One-Click Grid-Resource Model                                                                           | 96 |

| Optimizing Performance of Automatic Training Phase for Application Performance Prediction in the Grid       | )9 |

| Multiobjective Differential Evolution for Mapping in a Grid Environment                                     | 22 |

| Latency in Grid over Optical Burst Switching with Heterogeneous  Traffic                                    | 34 |

# High-Performance Scientific and Engineering Computing

| A Block JRS Algorithm for Highly Parallel Computation of SVDs  Mostafa I. Soliman, Sanguthevar Rajasekaran, and Reda Ammar                                             | 346        |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| Concurrent Number Cruncher: An Efficient Sparse Linear Solver on the GPU                                                                                               | 358        |

| Adaptive Computation of Self Sorting In-Place FFTs on Hierarchical Memory Architectures                                                                                | 372        |

| Parallel Multistage Preconditioners Based on a Hierarchical Graph Decomposition for SMP Cluster Architectures with a Hybrid Parallel Programming Model  Kengo Nakajima | 384        |

| High Performance FFT on SGI Altix 3700                                                                                                                                 | 396        |

| Security Enhancement and Performance Evaluation of an Object-Based Storage System                                                                                      | 408        |

| Languages and Compilers for HPC                                                                                                                                        |            |

| Strategies and Implementation for Translating OpenMP Code for Clusters                                                                                                 | 420        |

| Optimizing Array Accesses in High Productivity Languages                                                                                                               | 432        |

| ,,                                                                                                                                                                     |            |

| Software Pipelining for Packet Filters                                                                                                                                 | 446        |

| Software Pipelining for Packet Filters                                                                                                                                 | 446<br>460 |

| Software Pipelining for Packet Filters                                                                                                                                 |            |

| Efficient Broadcasting in Multi-radio Multi-channel and Multi-hop Wireless Networks Based on Self-pruning   | 484 |

|-------------------------------------------------------------------------------------------------------------|-----|

| Li Li, Bin Qin, Chunyuan Zhang, and Haiyan Li                                                               |     |

| Open Box Protocol (OBP)                                                                                     | 496 |

| Stability Aware Routing: Exploiting Transient Route Availability in MANETs                                  | 508 |

| Reliable Event Detection and Congestion Avoidance in Wireless Sensor Networks                               | 521 |

| Systolic Routing in an Optical Ring with Logarithmic Shortcuts Risto T. Honkanen and Juha-Pekka Liimatainen | 533 |

| Parallel/Distributed Architectures                                                                          |     |

| On Pancyclicity Properties of OTIS Networks                                                                 | 545 |

| MC2DR: Multi-cycle Deadlock Detection and Recovery Algorithm for Distributed Systems                        | 554 |

| FROCM: A Fair and Low-Overhead Method in SMT Processor                                                      | 566 |

| A Highly Efficient Parallel Algorithm for H.264 Encoder Based on Macro-Block Region Partition               | 577 |

| Towards Scalable and High Performance I/O Virtualization – A Case Study                                     | 586 |

| Peer-to-Peer Computing                                                                                      |     |

| A Proactive Method for Content Distribution in a Data Indexed DHT  Overlay                                  | 599 |

| CDACAN: A Scalable Structured P2P Network Based on Continuous  Discrete Approach and CAN  Lingwei Li, Qunwei Xue, and Deke Guo | 611 |

|--------------------------------------------------------------------------------------------------------------------------------|-----|

| Multi-domain Topology-Aware Grouping for Application-Layer                                                                     |     |

| Multicast                                                                                                                      | 623 |

| A Generic Minimum Dominating Forward Node Set Based Service Discovery Protocol for MANETs                                      | 634 |

| Performance, Evaluation and Measurements Tools                                                                                 |     |

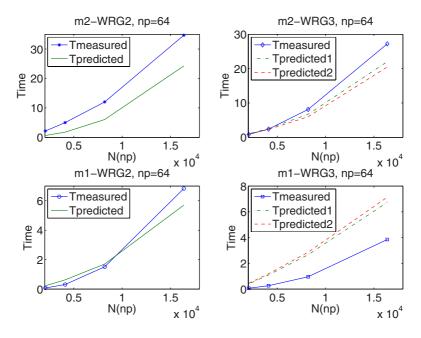

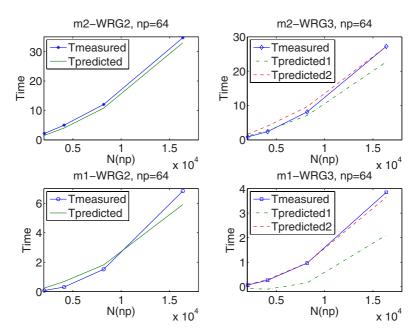

| Parallel Performance Prediction for Multigrid Codes on Distributed Memory Architectures                                        | 647 |

| Netgauge: A Network Performance Measurement Framework                                                                          | 659 |

| Towards a Complexity Model for Design and Analysis of PGAS-Based Algorithms                                                    | 672 |

| An Exploration of Performance Attributes for Symbolic Modeling of Emerging Processing Devices                                  | 683 |

| Towards Scalable Event Tracing for High End Systems                                                                            | 698 |

| Checkpointing Aided Parallel Execution Model and Analysis Laura Mereuta and Éric Renault                                       | 707 |

| Throttling I/O Streams to Accelerate File-IO Performance Seetharami Seelam, Andre Kerstens, and Patricia J. Teller             | 718 |

| Reliability and Fault-Tolerance                                                                                                |     |

| A Fast Disaster Recovery Mechanism for Volume Replication Systems                                                              | 732 |

| Dynamic Preemptive Multi-class Routing Scheme Under Dynamic Traffic in Survivable WDM Mesh Networks                            | 74  |

| Table of Con-                                                                                 | tents AIA |

|-----------------------------------------------------------------------------------------------|-----------|

| Quantification of Cut Sequence Set for Fault Tree Analysis                                    |           |

| Improving a Fault-Tolerant Routing Algorithm Using Detailed Tra<br>Analysis                   |           |

| Web Services and Internet Computing                                                           |           |

| An Ontology for Semantic Web Services                                                         | 776       |

| DISH - Dynamic Information-Based Scalable Hashing on a Cluster Web Cache Servers              |           |

| FTSCP: An Efficient Distributed Fault-Tolerant Service Composite Protocol for MANETs          | 797       |

| CIVIC: A Hypervisor Based Virtual Computing Environment Jinpeng Huai, Qin Li, and Chunming Hu | 809       |

| Author Index                                                                                  | 821       |

## Programming Challenges for Petascale and Multicore Parallel Systems

Vivek Sarkar

Rice University vsarkar@cs.rice.edu

**Abstract.** This decade marks a resurgence for parallel computing with high-end systems moving to petascale and mainstream systems moving to multi-core processors. Unlike previous generations of hardware evolution, this shift will have a major impact on existing software. For petascale, it is widely recognized by application experts that past approaches based on domain decomposition will not scale to exploit the parallelism available in future high-end systems. For multicore, it is acknowledged by hardware vendors that enablement of mainstream software for execution on multiple cores is the major open problem that needs to be solved in support of this hardware trend. These software challenges are further compounded by an increased adoption of high performance computing in new application domains that may not fit the patterns of parallelism that have been studied by the community thus far. In this talk, we compare and contrast the software stacks that are being developed for petascale and multicore parallel systems, and the challenges that they pose to the programmer. We discuss ongoing work on high productivity languages and tools that can help address these challenges for petascale applications on high-end systems. We also discuss ongoing work on concurrency in virtual machines (managed runtimes) to support lightweight concurrency for mainstream applications on multicore systems. Examples will be give from research projects under way in these areas including PGAS languages (UPC, CAF), Eclipse Parallel Tools Platform, Java Concurrency Utilities, and the X10 language. Finally, we outline a new long-term research project being initiated at Rice University that aims to unify elements of the petascale and multicore software stacks so as to produce portable software that can run unchanged on petascale systems as well as a range of homogeneous and heterogeneous multicore systems.

# Towards Enhancing OpenMP Expressiveness and Performance

Haoqiang Jin

NASA Ames Research Center hjin@nas.nasa.gov

Abstract. Since its introduction in 1997, OpenMP has become the de facto standard for shared memory parallel programming. The notable advantages of the model are its global view of memory space that simplifies programming development and its incremental approach toward parallelization. However, it is very challenge to scale OpenMP codes to tens or hundreds of processors. This problem becomes even more profound with the recent introduction of multicore, multi-chip architectures. Several extensions have been introduced to enhance OpenMP expressiveness and performance, including thread subteams and workqueuing. In this talk, we describe applications that expose the limitation of the current OpenMP and examine the impact of these extensions on application performance. We focus on exploiting multi-level parallelism and dealing with unbalanced workload in applications with these extensions and compare with other programming approaches, such as hybrid. Our experience has demonstrated the importance of the new language features for OpenMP applications to scale well on large shared memory parallel systems.

# Bandwidth-Aware Design of Large-Scale Clusters for **Scientific Computations**

#### Mitsuhisa Sato

Center for Computational Sciences, University of Tsukuba msato@cs.tsukuba.ac.jp

Abstract. The bandwidth of memory access and I/O, network is the most important issue in designing a large-scale cluster for scientific computations. We have been developing a large scale PC cluster named PACS-CS (Parallel Array Computer System for Computational Sciences) at Center for Computational Sciences, University of Tsukuba, for wide variety of computational science applications such as computational physics, computational material science, etc. For larger memory access bandwidth, a node is equipped with a single CPU which is different from ordinary high-end PC clusters. The interconnection network for parallel processing is configured as a multi-dimensional Hyper-Crossbar Network based on trunking of GigabitEthernet to support large scale scientific computation with physical space modeling. Based on the above concept, we are developing an original mother board to configure a single CPU node with 8 ports of Gigabit Ethernet, which can be implemented in the half size of 19 inch rack-mountable 1U size platform. PACS-CS started its operation on July 2006 with 2560 CPUs and 14.3 TFops of peak performance. Recently, we have newly established an alliance to draw up the specification of a supercomputer, called Open Supercomputer Specification. The alliance consists of three Japanese universities: University of Tsukuba, University of Tokyo, and Kyoto University (T2K alliance). The Open Supercomputer Specification defines fundamental hardware and software architectures on which each university will specify its own requirement to procure the next generation of their supercomputer systems in 2008. This specification requests the node to be composed of commodity multicore processors with high aggregated memory bandwidth, and the bandwidth of internode communication to be 5 GB/s or more in physical link level and 4 GB/s or more in MPI level with Link aggregation technology using commodity fabric. We expect several TFlops in each system. In order to support scalable scientific computations in a large-scale cluster, the bandwidth-aware design will be important.

## OpenMP 3.0 – A Preview of the Upcoming Standard

## Larry Meadows

Intel Corporation

lawrence.f.meadows@intel.com

**Abstract.** The OpenMP 3.0 standard should be released for public comment by the time of this conference. OpenMP 3.0 is the first major upgrade of the OpenMP standard since the merger of the C and Fortran standards in OpenMP 2.5. This talk will give an overview of the new features in the OpenMP standard and show how they help to extend the range of problems for which OpenMP is suitable.

Even with multi-core, the number of hardware cores in an SMP node is likely to be relatively small for the next few years. Further, a number of users want to use OpenMP, but need to scale to more cores than fit in a node, and do not want to mix OpenMP and MPI. Intel supports a production quality OpenMP implementation for clusters that provides a way out. This talk will briefly introduce Intel Cluster OpenMP, provide an overview of the tools available for writing programs, and show some performance data.

## Manycores in the Future

## Robert Schreiber

HP Labs rob.schreiber@hp.com

**Abstract.** The change from single core to multicore processors is expected to continue, taking us to manycore chips (64 processors) and beyond. Cores are more numerous, but not faster. They also may be less reliable. Chip-level parallelism raises important questions about architecture, software, algorithms, and applications. I'll consider the directions in which the architecture may be headed, and look at the impact on parallel programming and scientific computing.

## The Changing Impact of Semiconductor Technology on Processor Architecture

Ray Simar

Texas Instruments r-simar@ti.com

**Abstract.** We stand on the brink of a fundamental discontinuity in silicon process-technology unlike anything most of us have seen. For almost two decades, a period of time spanning the entire education and careers of many engineers, we have been beneficiaries of a silicon process-technology which would let us build almost anything we could imagine. Now, all of that is about to change. For the past five years, capacitive loading of interconnect has grown to be a significant factor in logic speed, and has limited the scaling of integrated-circuit performance. To compound the problem, recently interconnect resistance has also started to limit circuit speed. These factors can render obsolete current designs and current thinking as interconnect-dominated designs and architectures will become increasingly irrelevant. Given these fundamental interconnect challenges, we must turn to architecture, logic design and programming solutions. The background on these dramatic changes in semiconductor technology will be discussed in the hopes that the solutions for the future may very well come from the attendees of HPCC 2007!

## A Windows-Based Parallel File System

Lungpin Yeh, Juei-Ting Sun, Sheng-Kai Hung, and Yarsun Hsu

Department of Electrical Engineering,

National Tsing Hua University HsinChu, 30013, Taiwan

{lungpin,posh,phinex}@hpcc.ee.nthu.edu.tw, yshsu@ee.nthu.edu.tw

Abstract. Parallel file systems are widely used in clusters to provide high performance I/O. However, most of the existing parallel file systems are based on UNIX-like operating systems. We use the Microsoft .NET framework to implement a parallel file system for Windows. We also implement a file system driver to support existing applications written with Win32 APIs. In addition, a preliminary MPI-IO library is also developed. Applications using MPI-IO could achieve the best performance using our parallel file system, while the existing binaries could benefit from the system driver without any modifications. In this paper, the design and implementation of our system are described. File system performance using our preliminary MPI-IO library and system driver is also evaluated. The results show that the performance is scalable and limited by the network bandwidth.

## 1 Introduction

As the speed of CPU becomes faster, we might expect that the performance of a computer system should benefit from the advancement. However, the improvements of other components in a computer system (i.e. memory system, data storage system) cannot catch up with that of CPU. Although the capacity of a disk has grown with time, its mechanical nature limits its read/write performance. In this data-intensive world, it is significant to provide a large storage subsystem with high performance I/O[1]. Using a single disk with a local file system to sustain this requirement is impossible nowadays. Disks combined either tightly or loosely to form a parallel system provide a possible solution to this problem. The success of a parallel file system comes from the fact that accessing files through network can have higher throughput than fetching files through local disks. This could be attributed to the emergence of high-speed networks such as Myrinet [2], InfiniBand [3], Gigabit Ethernet, and more recently 10 Gigabit Ethernet.

A parallel file system can not only provide a large storage space by combining several storage resources on different nodes but also increase the performance. It could provide high-speed data access by using several disks at the same time. With suitable striping size, the workload in the system can be distributed among these disks instead of being centralized in a single disk. For example, whenever a write happens, a parallel file system would split these data into a lot of small

R. Perrott et al. (Eds.): HPCC 2007, LNCS 4782, pp. 7–18, 2007.

<sup>©</sup> Springer-Verlag Berlin Heidelberg 2007

chunks, which are then stored on different disks across the network in a round-robin fashion.

Most of parallel file systems are based on Unix or Linux. As far as we know, WinPFS[4] is the only parallel file system based on Microsoft Windows. However, it does not allow users to specify the striping size of a file across nodes. Furthermore, it does not provide a user level library for high performance parallel file access. In this paper, we implement a parallel file system for Microsoft Windows Server 2003 allowing users the flexibility to specify different striping size. Users can specify the striping size to satisfy the required distribution or using the default striping size provided by the system. We have implemented a file system driver to trap Win32 APIs such that existing binaries can access files stored on our parallel file system without recompilation. Besides, some MPI-IO functions (such as noncontiguous accesses) are also provided for MPI jobs to achieve the best performance. We have successfully used our parallel file system as a storage system for VOD (Video On Demand) services, which can deliver the maximum bandwidth and demonstrate the successful implementation of our parallel file system.

This paper is organized as follows: Section 2 presents some related works. Design and implementation will be discussed in section 3, with the detailed description of our system driver. Section 4 depicts the results of performance evaluation of our windows-based parallel file system, along with the prototype VOD system. Finally, we would make some conclusions and provide some directions in section 5.

## 2 Related Works

PVFS[5,6] is a parallel file system publicly available in the Linux environment. It provides both user level library for performance and a kernel module package that makes existing binaries working without recompiling.

WinPFS [4] is a parallel file system for Windows and integrated within the Windows kernel components. It uses the existing client and server pairs in the Windows platform (i.e. NFS [7], CIFS [8], ...) and thus no special servers are needed. It also provides a transparent interface to users, just like what does when accessing normal files. The disadvantage is that the user can not specify the striping size of a file across nodes. Besides, its performance is bounded by the slowest client/server pairs if the load balancing among servers is not optimal. For example, if it uses NFS as one of the servers, the overall performance may be gated by NFS. This heterogeneous client/server environment helps but it might also hurt when encountering unbalanced load.

Microsoft adds the support of dynamic disks starting from Windows 2000. Dynamic disks are the disk formats in Windows necessary for creating multi-partition volumes, such as spanned volumes, mirrored volumes, striped volumes, and RAID-5 volume. The striped volumes contain a series of partitions with one partition per disk. However, only up to 32 disks can be supported, which is not very scalable[9].

## 3 Design and Implementation

The main task of the parallel file system is to stripe data or split files into several small pieces. Files are equally distributed among different I/O nodes and can be accessed directly from applications. Applications can access the same file or different files in parallel rather than sequentially. The more I/O nodes in a system, the more bandwidth it could provide (only limited by the network capacity).

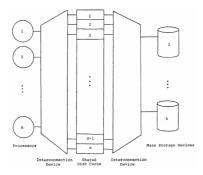

## 3.1 System Architecture

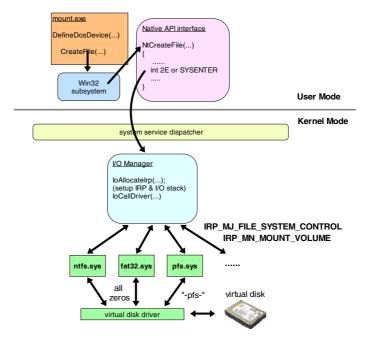

Generally speaking, our parallel file system consists of four main components: Metadata server, I/O daemons (Iod), a library and a file system driver. Metadata server and I/O daemons set up the basic parallel file system architecture. The library provides high performance APIs for users to develop their own applications on top of the parallel file system. It communicates with the metadata server and Iods, and does the tedious work for users. The complexity behind the parallel file system is hidden by the library and users do not need to concern about how the metadata server and Iods co-operate. With the help of file system driver, we can trap I/O related Win32 API calls and provide transparent file accesses. Most of the user mode APIs have the kernel mode equivalent implementation. The overall architecture is shown in Fig. 1.

Fig. 1. The overall system architecture

Metadata Server. Metadata means the information about a file except for the contents that it stores. In our parallel file system, metadata contains five parts:

- File size: It describes the size of a file.

- File index: It is a 64-bit number, which uniquely identifies the file stored on the metadata server. Its uniqueness is maintained by the underlying file system, such as the inode number of the UNIX operating systems. It is used as the filename of the striped data stored on I/O nodes.

- Striping size: The size that a file is partitioned.

- Node count: The number of I/O nodes that the file is spread across.

- Starting I/O node: The I/O node that the file is first stored on.

The metadata server runs on a single node, managing the metadata of a file and maintaining the directory hierarchy of our parallel file system. It does not communicate with I/O daemons or users directly, but only converses with the library, libwpvfs. Whenever a file is requested, users may call the library to connect with the metadata server and get the metadata of that file. Before a file can be accessed, its metadata must be fetched in advance.

I/O Daemons. The I/O daemon is a process running on each of the I/O nodes responsible for accessing the real data of a file. It can run on a single node or several nodes, and you can run several I/O daemons on an I/O node if you want. After users get the metadata of a file, the library could connect to the required I/O nodes, and the Iods would access the requested file and send stripes back to the client.

Each of the I/O nodes maintains a flat directory hierarchy. The file index is used as the filename of the striped data regardless of the file's real filename. No matter what the real path of a file is, the striped data is always stored in a directory whose name is hashed from the file index. In our implementation, we use modulation as the hash function.

### 3.2 Library

As mentioned before, a library can hide the complexity of a parallel from users. In this subsection, we would discuss how the different libraries are implemented.

User Level Library. We provide a class library that contains six most important file system methods, including open, create, read, write, seek, and close. These methods are mostly similar to those of the File class in C# but with more capabilities support. Users can specify the striping size, starting Iod, and Iod counts when accessing a file. The library separates the users from the Iods and the metadata server. All the tedious jobs will be handled by the library. With the help of the library, users only need to concern how to efficiently partition and distribute the file.

Kernel Level File System Driver. In the Windows operating system, NT I/O Manager, which is a kernel component, is responsible for the I/O subsystem. To allow I/O Manager and drivers to communicate with other components in the operating system, a data structure called I/O Request Packet (IRP) is frequently used. An IRP contains lots of information to describe requests and parameters. Most import of all is the major function code and the minor function code. These two integers contained in an IRP precisely indicate the operation that should be performed. I/O related Win32 APIs will eventually be sent to the I/O Manager, which then allocates an IRP sent to the responsible driver.

With the help of a virtual disk driver, a file system driver, and a mount program, our parallel file system can be mounted as a local file system for Windows. Fig. 2 illustrates the mounting process of our parallel file system. The virtual disk driver presents itself as a normal hard disk to Windows when it is loaded into the system. The mount program invokes the <code>DefineDosDevice</code> function call to create a new volume on the virtual disk. After the new volume is created, the mount program tries to create a file on the volume. This request will be routed to the NT I/O Manager. Upon receiving this request, the I/O Manager finds that this volume is not handled by any file system driver yet. Thus, it sends an IRP containing a mount request to each of registered file system drivers in the system. File system drivers check the on disk information when they receive such a request to determinate if it recognizes this volume.

We implement a crafted read function in the virtual disk driver. The driver returns a magic string "-pfs-" without quotes when a file system driver tries

Fig. 2. The process of mounting our parallel file system

to read 6 bytes from the disk. Otherwise, it returns zeros. In this way, while any other file system drivers try to check the on disk information, they do not recognize the volume. "-pfs-" is the magic string that only our parallel file system driver recognizes. When the mount request is sent to our file system driver, it reads 6 bytes from the disk, recognizes the magic string, and tells the I/O Manager that this volume is under our control. The mount operation completes and all I/O operations targetting at this volume will be routed to our file system driver hereafter.

On loading the file system driver into the system, persistent connections are established to all I/O daemons. The connection procedures are performed once at the loading time, and all operations are made through these sockets. This eliminates the connection overhead of all I/O operations from user mode applications. The file system driver effectively does the same thing as the user mode library when it receives a read or write operation.

MPI-IO Library. MPI-IO[10] is the parallel I/O part of MPI and its objective is to provide high performance parallel I/O interface for parallel MPI programs. A great advantage of MPI-IO is the ability to access noncontiguous data with a single function call, which is known as collective I/O. Our parallel file system is built on .NET framework using C#.

#### 4 Performance Evaluation

In this section, the local file system performance is measured along with read and write performance of our parallel file system. The hardware used is IBM eServer xSeries 335 with five nodes connected through Gigabit Ethernet, each housing:

- One Intel Xeon processor at 2.8 GHz

- 512 MB DDR memory

- 36.4 G Ultra 320 SCSI disk

- Microsoft Windows Server 2003 SP1

## 4.1 Local File System Performance

Our parallel file system doesn't maintain the on disk information itself, but relies on the underlying file system. The root directory for Iods or the metadata server is set in an NTFS partition. To test I/O performance of the local file system and the .NET framework, we write a simple benchmark using C#. The tests are performed on a single node, running the tests ten times and averaged the results.

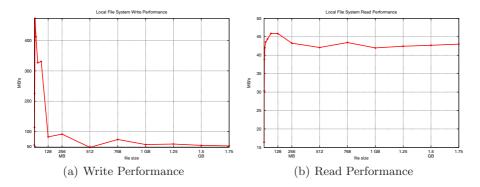

A 64 KB buffer is filled with random data and written to the local file system continuously until the number of bytes written to the local file system reaches the file size. Note that the write operations are carried out by the Microsoft .NET Framework and the NTFS file system driver which has some caching mechanism

Fig. 3. Performance evaluation of local file system

internally. In Fig. 3(a), we observe that write performance of local file system converges to about 55 MB/s when the file size is larger than 768 MB, but the performance varies when the file size is smaller than 512 MB. We think this is the effect of the caching mechanism.

To make sure that the files written are not cached in memory, the system is rebooted before measuring the read performance. The same file is read from the disk into a fixed-size buffer and the buffer is used over and over again. The data read is ignored and overwritten by later reads. As you can see from Fig. 3(b), read performance converges to about 43 MB/s.

## 4.2 Performance Evaluation Using User Level Library

The performance of our parallel file system are evaluated on five nodes. One of them is served both as a metadata server and a client which runs our benchmark program written with our library. The other four nodes are running I/O daemons, one for each.

Again, a fixed-size memory buffer is filled with random data. After that, a create operation is invoked, and the buffer content is written to the parallel file system continuously until the number of bytes written reaches the file size. The test program then waits for the acknowledgements sent by the I/O daemons to make sure all the data sent by the client are received by all I/O daemons. Note that though the Iods have written received data to their local file systems, this does not guarantee that the data is really written to their local disks. They may be cached in the memory by the operating system and written back to the physical disks later. We ran the tests ten times and averaged the results.

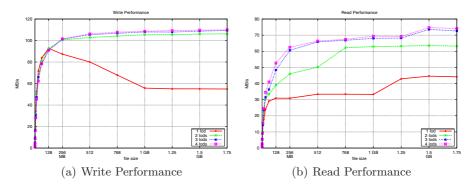

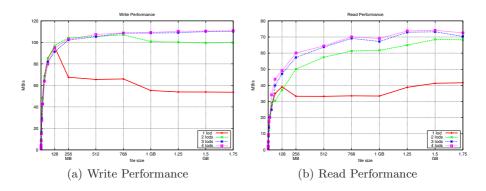

In Fig. 4(a), we measure write performance with various file sizes and various number of I/O nodes. The striping size is 64 KB. The size of the memory buffer used equals to the number of I/O nodes multiplied by the striping size. Write performance converges to about 53 MB/s when only one I/O node is used. We consider that the write performance is bounded by the local file system in this case, since this is almost equal to the local file system write performance as

shown in the previous test. The performance of writing to two I/O nodes is about twice of writing to only one node when the file size is large enough.

However, write performance reaches a peak of 110 MB/s when writing to three or four I/O nodes. For these two cases, they almost have the same performance since the bottleneck is the network bandwidth rather than the physical disks. Since all the cluster nodes are connected by a Gigabit Ethernet which has the theoretical peak bandwidth of 125 MB/s, it is conceivable that a client can not write out faster than 125 MB/s due to protocol overhead. The same behavior has been observed in PVFS[11] and IBM vesta parallel file system[12]. However, we expect the write performance to be scalable if a higher bandwidth network is available in the future.

The size of the memory buffer for read is also the number of I/O nodes multiplied by the striping size. The data read into the memory buffer is ignored and overwritten by later data. As you can see in Fig. 4(b), read performance is not as good as write performance. But when we increase the number of I/O nodes, the performance increases too. For four I/O nodes, read performance reaches a peak of 75 MB/s. With the use of more than two I/O nodes, read performance of our parallel file system is better than that of a local disk.

We have made some tests to figure out why the read performance can not fully utilize the theoretical network bandwidth. The Iod program is modified such that when it receives a read request, it does not read the data from the local file system, but just sends the contents of a memory buffer to the client directly. The contents in the memory buffer are non-deterministic. In this process of measuring read performance, the behavior is exactly the same as previous tests except that no local file system operations are involved. We run the test several times. The results show that when only one I/O node is used, the curves are almost identical and the performance reaches a peak of 90 MB/s. In the case of two I/O nodes, it has the same behavior but the performance reaches a peak of 93 MB/s. For three and four I/O nodes, the curves are desultory and the average performance reaches a peak of around 78 MB/s which is lower than the performance of using only one or two I/O nodes. We think this is due to network congestion and packet collision. Whenever multiple I/O nodes try to send large

Fig. 4. Performance evaluation using variable I/O nodes

amount of data to a client simultaneously, the receiving speed of the client can not catch up with the overall sending speed of I/O nodes. Therefore some packets may collide with others and get dropped. The I/O nodes have to back off and resend packets as required by the protocol design of Ethernet architecture. This explains why the read performance is not as good as the write performance and saturated around 75 MB/s when three or four I/O nodes are used. In Fig. 4(b), the read performance of one I/O node and two I/O nodes are bounded by the local file system. In the case of three and four I/O nodes, it is bounded by the network due to network congestion. Again, as in write performance, we expect the read performance to be improved significantly when a higher performance network is available in the future.

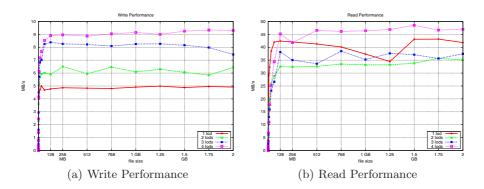

## 4.3 Performance Evaluation Using Kernel Driver

To measure the performance of our parallel file system when using the file system driver, we write a simple benchmark program which has the same functionality as the one written in C#. But this benchmark uses Win32 APIs directly to create, read and write files. We also repeat the tests ten times and average the results.

Fig. 5(a) shows the write performance with various number of I/O nodes. The striping size is 64 KB and the user supplied memory buffer is 1 MB. When we increase the number of I/O nodes, the performance increases too, but it is worse than that of the local file system even when four I/O nodes are used. As observed from Fig. 5(b), the read performance is much better compared with the write performance. The performance increases with the number of I/O nodes when more than two I/O nodes are used, but the performance with only one I/O node is between that of four I/O nodes and three I/O nodes.

Windows is a commercial product and the source codes are not available. Therefore, the detail operations are opaque. Furthermore the file system driver resides in kernel mode and needs a socket library to communicates with daemons in the parallel file system. Microsoft doesn't provide a socket library for kernel

Fig. 5. Performance evaluation using the system driver with 64KB striping size and 1MB user buffer

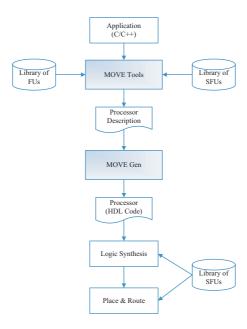

mode programmers. The lack of a sophisticated kernel mode socket library also makes it difficult to write high performance programs.

The main purpose of implementing a kernel driver is to enable existing binaries to run over this parallel file system. However the parallel file system is developed mainly for high performance applications. We expect users to write high performance applications using our new APIs created especially to take advantage of this parallel file system.

## 4.4 Performance Evaluation Using MPI-IO

We use the MPI-IO functions that we have implemented to write a benchmark program. In this case, we set the size of etype[10] to 64 KB which is equal to the striping size of the previous three cases. This is an obvious selection, since an etype (elementary datatype) is the basic unit of data access and all file accesses are performed in units of etype. The visible portion of the filetype is set to an etype and the stride[10] (i.e. the total length of the filetype) is set to the number of I/O nodes multiplied by the etype. Finally, the displacement is set to the rank of the I/O node multiplied by the etype. All the others are set based on the previous settings.

We measure the performance by varying the number of I/O nodes from one to four. The buffer size is set to be the number of I/O nodes multiplied by the etype. Each test is performed ten times and averaged to get the final result. The write and read performance are shown in Fig. 6(a) and Fig. 6(b) respectively.

The trends of the write and read performance resemble those which we have discussed above. Compared with the library of our parallel file system, libwpvfs, the MPI-IO functions have some added function calls and operations, but they do not influence the performance deeply. Consequently, the MPI-IO functions are provided without suffering serious overhead.

Fig. 6. Performance evaluation using our MPI-IO library

## 4.5 VOD Prototype System

Besides, we have set up a distributed multimedia server on top of our parallel file system. Microsoft DirectShow is used to build a simple media player. Using DirectShow with libwpvfs, we build a media player, which could play multimedia files distributed across different I/O nodes. Since DirectShow can only play media files stored on disks or from a URL, we establish a web server as an agent to gather striped files from I/O nodes. This web server is inserted between the media player and our library, libwpvfs, and it is the web server that uses the library to communicate with the metadata server and I/O nodes.

The data received by the web server from I/O nodes is passed to the media player. The media player plays a media file coming from the http server through a URL rather than from the local disk. Both the media player and the web server run on the local host. The web server is bound with our media player and transparent to the end user. A user is not aware of the existence of the web server and could use our media player as a normal one.

Any existing media player programs which support playing media files from an URL, such as Microsoft Media Player, can take advantage of our parallel file system by accessing the video file on our web server. In this way, we may provide a high performance VOD service above our parallel file system.

#### 5 Conclusions and Future Work

PC-based clusters are getting more and more popular these days. Unfortunately almost all of the parallel file systems are developed in UNIX-based clusters. It is hard to implement a Windows-based parallel file system because Windows is a commercial product and the source codes are not available. In this paper, we have implemented a parallel file system which provides parallel I/O operations for PC clusters running Windows operating system. A user mode library using .NET framework is also developed to enable users writing efficient parallel I/O programs. We have also successfully implemented a simple VOD system to demonstrate the feasibility and usefulness of our parallel file system. In addition we have implemented key MPI-IO functions on top of our parallel file system and found that the overhead of implementing MPI-IO is very minimal. The performance of MPI-IO is very close to the performance provided by the parallel file system. Furthermore, we have also implemented a file system driver which provides a transparent interface for accessing files stored on our parallel file system so that existing programs written with Win32 APIs can still run on our system.

We have found that both write and read performance are scalable and only limited by the performance of the Ethernet network we use. We plan to further evaluate the performance of this parallel file system when we can obtain a higher performance network such as Infiniband under Windows and believe that our parallel file system can automatically achieve much better performance.

The prototyping VOD system proves the usability of our parallel file system in the Windows environment. Varying the striping size in the VOD system under different load conditions may have distinct behavior. The impact of the striping size may hurt or help the VOD system under different load conditions. We would perform some detailed experiments and analysis in the near future. This would help us develop a more realistic and high performance VOD system that can benefit from our parallel file system.

## References

- Adiga, N.R., Blumrich, M., Liebsch, T.: An overview of the BlueGene/L supercomputer. In: Proceedings of the 2002 ACM/IEEE Conference on Supercomputing, Baltimore, Maryland, pp. 1–22 (2002)

- 2. Myricom: Myrinet, http://www.myri.com/

- 3. InfiniBand Trade Association: Infiniband, http://www.infinibandta.org/

- Pérez, J.M., Carretero, J., García, J.D.: A Parallel File System for Networks of Windows Worstations. In: ACM International Conference on Supercomputing (2004)

- Carns, P.H., Ligon III, W.B., Ross, R.B., Thakur, R.: PVFS: A parallel file system for linux clusters. In: 4th Annual Linux Showcase and Conference, Atlanta, GA, pp. 317–327 (2000)

- 6. Ligon III, W. B., Ross, R.B.: An Overview of the Parallel Virtual File System. In: 1999 Extreme Linux Workshop (1999)

- Kleiman, S., Walsh, D., Sandberg, R., Goldberg, D., Lyon, B.: Design and implementation of the sun network filesystem. In: Proc. Summer USENIX Technical Conf., pp. 119–130 (1985)

- 8. Hertel, C.R.: Implementing CIFS: The Common Internet File System. Prentice-Hall, Englewood Cliffs (2003)

- 9. Russinovich, M.E., Solomon, D.A.: Microsoft Windows Internals, Microsoft Windows Server 2003, Windows XP, and Windows 2000, 4th edn. Microsoft Press, Redmond (2004)

- Corbett, P., Feitelson, D., Fineberg, S., Hsu, Y., Netzberg, W., Prost, J., Snir, M., Traverset, W., Wong, P.: 32. In: Overview of the MPI-IO Parallel IO Interface. IEEE and Wiely Interscience, Los Alamitos (2002)

- Ligon III, W.B., Ross, R.B.: Implementation and performance of a parallel file system for high performance distributed applications. In: Proceedings of the Fifth IEEE International Symposium on High Performance Distributed Computing, pp. 471–480. IEEE Computer Society Press, Los Alamitos (1996)

- Feitelson, D.G., Corbett, P.F., Prost, J.-P.: Performance of the vesta parallel file system. In: 9th Internationl Parallel Processing Symposium, pp. 150–158 (1995)

## PARMI: A Publish/Subscribe Based Asynchronous RMI Framework for Cluster Computing

Heejin Son and Xiaolin Li

Scalable Software Systems Laboratory

Computer Science Department,

Oklahoma State University

Stillwater, OK 74078, U.S.A.

{hees,xiaolin}@cs.okstate.edu

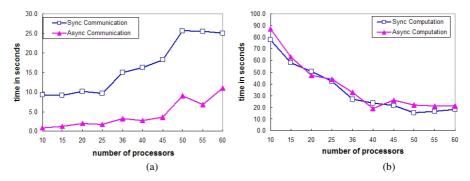

Abstract. This paper presents a publish/subscribe based asynchronous remote method invocation framework (PARMI) aiming to improve performance and programming flexibility. PARMI enables high-performance communication among heterogeneous distributed processors. Based on publish/subscribe paradigm, PARMI realizes asynchronous communication and computation by decoupling objects in space and time. The design of PARMI is motivated by the needs of scientific applications that adopt asynchronous iterative algorithms. An example scientific application based on the Jacobi iteration numerical method is developed to verify our model and evaluate the system performance. Extensive experimental results on up to 60 processors demonstrate the significant communication speedup using asynchronous computation and communication technique based on the PARMI framework compared to a baseline scheme using synchronous iteration and communication.

## 1 Introduction

Large scale distributed computing is complicated and poses a significant challenge due to its scale, dynamics, and heterogeneity. Traditional solutions like RPC (remote procedure call) gained popularity due to widely available built-in libraries. But RPC offers limited capabilities because it supports only C/C++ and Fortran programming languages and primitive point-to-point communication. The goal of this study is to provide a flexible programming tool based on publish/subscribe paradigm for parallel and distributed applications with decoupled communication and asynchronous computation.

Our contributions include: (1) design and develop the PARMI framework to enable scalable asynchronous computation and communication; (2) adopt the publish/subscribe paradigm to enhance the existing remote method invocation (RMI) in Java by enabling asynchronous RMI; (3) make use of the recently introduced generics mechanism in Java to enable flexible interfaces to support dynamic applications and parameterized classes and objects.

The rest of this paper is organized as follows. Section 2 presents the motivation and related work. Section 3 presents the system architecture of the overall design of

the PARMI including main features. Section 4 presents and analyses the experimental results and evaluates its performance. Finally, Section 5 concludes this paper.

#### 2 Related Work

Java has grown into a main-stream programming language since its inception. With the increasing adoption of Java for parallel and distributed computing, the built-in remote method invocation (RMI) mechanism is one of the most popular enabling solutions for parallel and distributed computing using Java [1]. Building on the popularity of RMI, we further enhance it with asynchronous communication, which is desirable to decouple sending/receiving objects and facilitate overlapping computation and communication. In PARMI, the publish/subscribe paradigm is used to decouple communicating parties in both time and space. Following the object-oriented programming paradigm, PARMI aims to provide a simple platform to support complex large-scale scientific applications.

The challenging issues are as follows: (1) how to overcome a synchronous and point-to-point communication nature of RMI, (2) how to provide a scalable framework for dynamic applications, and (3) how to maintain a strong decoupling of participants in both time and space.

#### 2.1 Shortcomings of Java RMI

The RMI system allows an object running in one Java virtual machine (JVM) to invoke methods on an object running in another JVM. A user can utilize a remote reference in the same manner as a local reference. However, the synchronous nature of RMI leads network latency and low-performance. Thus, several implementations have been developed that support extended protocols for RMI. These include Manta, NinjaRMI, and JavaParty by changing the underlying protocols such as the serialization protocols [2]. In 1997, Object System presented a communication system called Voyager, providing several communication modes allowing for synchronous invocation, asynchronous invocations with no reply (one way), and asynchronous invocation with a reply (future/promise) [3-6].

Asynchronous RMI with a Future Object. The RMI with a future object is the latest and most efficient means for providing asynchronous communication between a client and a server. A future object allows a client to continue computation after the incomplete communication without being blocked. Thanks to built-in classes and interfaces for the future object which holds a result of an asynchronous call, we don't need to spend time to implement the future object after Java version 1.5 or later. The previous asynchronous RMI studies have manipulated the stub class, which was generated automatically by an rmic compiler. Many difficulties in maintenance have occurred from this approach. For example, if a method that is invoked remotely by an object is modified, the corresponding classes and interfaces should be changed accordingly. After a stub class was generated by a RMIC compiler, we must change the stub class manually. Therefore, we focus on adding codes to access the FutureTask on the client side, not changing the stub class.

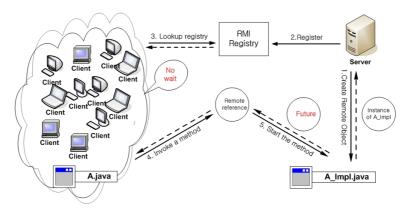

Fig. 1. Operation of the asynchronous RMI with a future object

Fig. 1 shows the operations of the asynchronous RMI with a future object. Several client-side processes send signals to invoke server-side methods. *A\_Impl* class has all business logics for methods of *A* interface. *A* interface has all method names available for remote invocation. Server program creates an instance of the *A\_Impl* class and binds the service with the RMI registry. Now, a client is able to get a remote reference from the RMI registry using lookup service. Once the client invokes a method, it proceeds with the remaining works without waiting because a future object is returned instantly when it is called.

This model overcomes synchronization but it is still tightly coupled in space and time [7].

#### 2.2 Publish/Subscribe Communication Model

In the publish/subscribe model, the information bus requires operating constantly and tolerating for dynamic system evolution and legacy system. Providers publish data to an information bus and consumers subscribe data they want to receive [8]. Providers and consumers are independent to each other and need not even know of their existence in advance. In general, the provider is also called the publisher, the consumer is the subscriber, and the information bus is the middleware or broker. In systems based on the publish/subscribe interaction paradigm, subscribers register their interests in an event or pattern of events, and are subsequently asynchronously notified of events generated by publishers [7].

As distributed systems on wide area networks grow, the demands of flexible, efficient, and dynamic communication mechanisms have increased. The publish/subscribe communication paradigm provides a many-to-many data dissemination. It is an asynchronous messaging paradigm that allows for better scalable and more dynamic network topology. The publish/subscribe interaction is an asynchronous messaging paradigm, characterized by the strong decoupling of participants in both time and space [9].

The classical categories of publish/subscribe communications are *topic-based* and *content-based* systems. In the topic-based system, messages are published to topics or named logical channels, which are hosted by a broker. Subscribers obtain all messages published to the topics to which they subscribe and all subscribers to the

topic will receive the same messages. Each topic is grouped by keywords. In the content-based system, messages are only delivered to a subscriber if the attributes or content of those messages match constraints defined by one or more of the subscriber's subscriptions. This method is based on tuple-based system. Subscribers can get a selective event using filter in form of name-value pairs of properties and basic comparison operators (=, >,  $\geq$ ,  $\leq$ ). However, these classical approaches have limited in designing the object-oriented system. They have considered the different models for the middleware and the programming language. Consequently, the object-oriented and message-oriented worlds often claimed to be incompatible [10]. Patrick T. Eugster presented *a type-based* publish/subscribe which can provide type safety and encapsulation [11].

## 3 PARMI System Architecture

#### 3.1 PARMI Framework

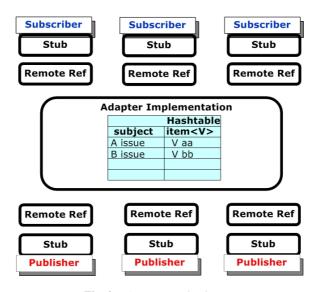

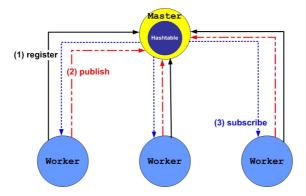

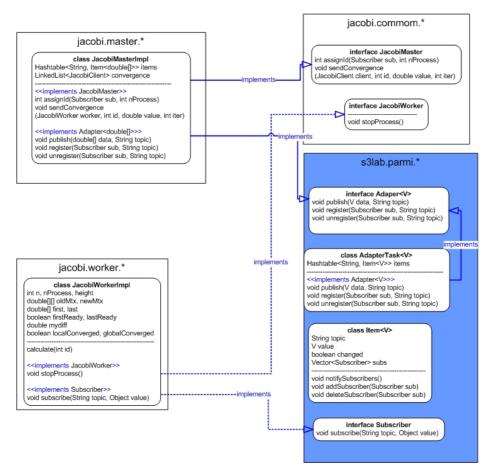

As shown in Fig. 2, PARMI consists of four main components: *publishers, subscribers, adapter,* and *items.* Publishers and subscribers preserve the stub/skeleton and the remote reference layer, because they use the same objects and methods from the RMI system. However, the adapter and items are designed particularly for the PARMI framework that enable the publish/subscribe communication.

The adapter is a central entity that keeps a set of all available items for publishers and subscribers in a hierarchical manner. The set is represented as a hashtable  $\in = \{x_1...x_m\}$ , where  $x_i$  is an item. The set has a unique topic as a key mapping with an item  $x_i$  for a value as hashtable. The adapter collects subscriptions and forwards events to subscribers. The adapter executes the same role as a server in the existing RMI system.

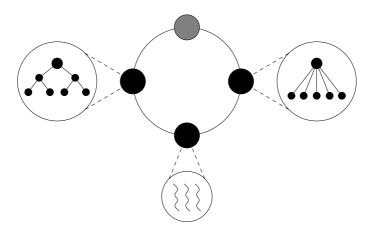

Fig. 2. PARMI organization

An item  $x_i$  is an element in the adapter holding the mapping information in three attributes: a topic as a String type, a value as a generic form  $\langle V \rangle$ , and a collection of subscribers' remote references  $\mathfrak{t} = \{S_1 \dots S_m\}$  interested in the topic. Generics enables type-safety and simple interfaces to create automated data objects[12].  $\langle V \rangle$  can be any type of object such as Integer, Boolean, Double, String, Arrays, or even Class. Whenever a corresponding event occurs, an item keeps adding or removing three attributes. When notifySubscribers method is locally invoked, it notifies all subscribe methods of each subscriber registered. And this mechanism was inspired by the observer-observable design pattern, which is also available in java.util.\* libraries in the form of interface Observer and class Observable.

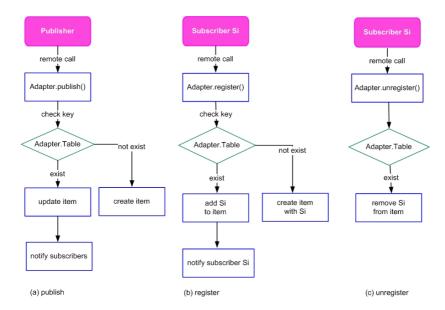

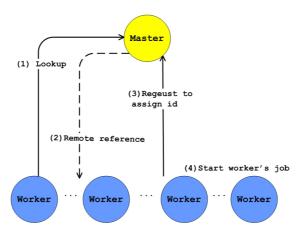

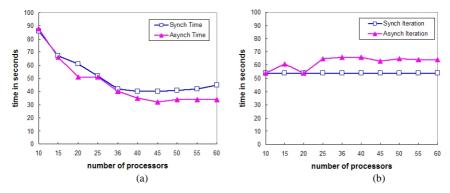

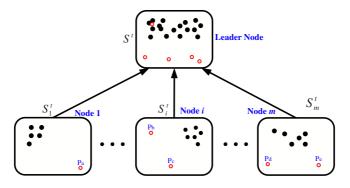

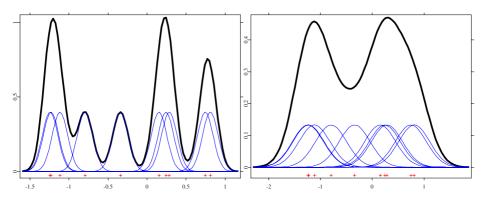

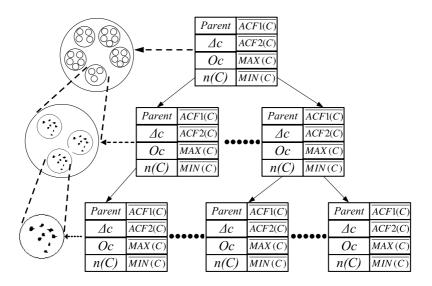

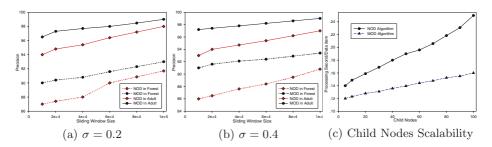

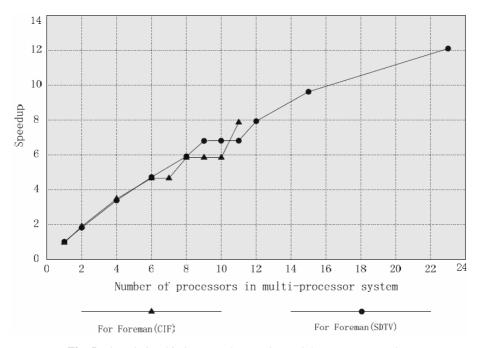

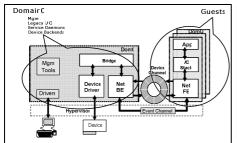

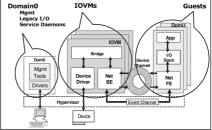

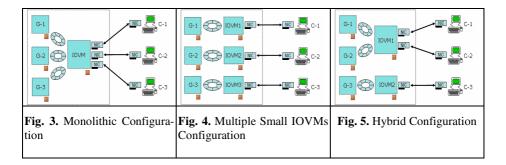

Fig. 3 shows operations in the PARMI system. If we have a set of processes,  $\Pi = \{p_1...p_n\}$  that communicate by exchanging information items, then each process  $p_i$  executes three operations:  $publish_i(v,t)$ ,  $register_i(S_i,t)$ , and  $unregister_i(S_i,t)$ , where v is a value of an information item, t is a topic for publish and subscribe, and S is a subscriber itself.